Can Slc500 Ch. 0 Registers

A wise PLC programmer once told me that the first thing any aspiring developer should learn about the PLC they intend to program is how the digital memory of that PLC is organized. This is sage advice for whatever programmer, peculiarly on systems where memory is limited, and/or where I/O has a fixed clan with certain locations in the arrangement's memory.

Virtually every microprocessor-based control system comes with a published memory map showing the organization of its limited memory: how much is available for certain functions, which addresses are linked to which I/O points, how different locations in memory are to be referenced past the programmer.

Detached input and output channels on a PLC correspond to individual bits in the PLC's memory assortment. Similarly, analog input and output channels on a PLC correspond to multi-fleck words (contiguous blocks of bits) in the PLC's memory.

The association between I/O points and retention locations is by no means standardized between different PLC manufacturers, or even between different PLC models designed past the same manufacturer. This makes it difficult to write a general tutorial on PLC addressing, and then my ultimate advice is to consult the engineering references for the PLC system you intend to program.

The most common make of PLC in use is Allen-Bradley (Rockwell), which happens to use a unique form of I/O addressing (Note ane), students tend to find confusing. For these two reasons (popularity and defoliation), I volition focus on Allen-Bradley addressing conventions for the majority of this department.

Note ane : The most mod Allen-Bradley PLCs accept all but done away with fixed-location I/O addressing, opting instead for tag proper noun based I/O addressing. However, enough legacy Allen-Bradley PLC systems notwithstanding exist in industry to warrant coverage of these addressing conventions.

PLC Retentiveness Map

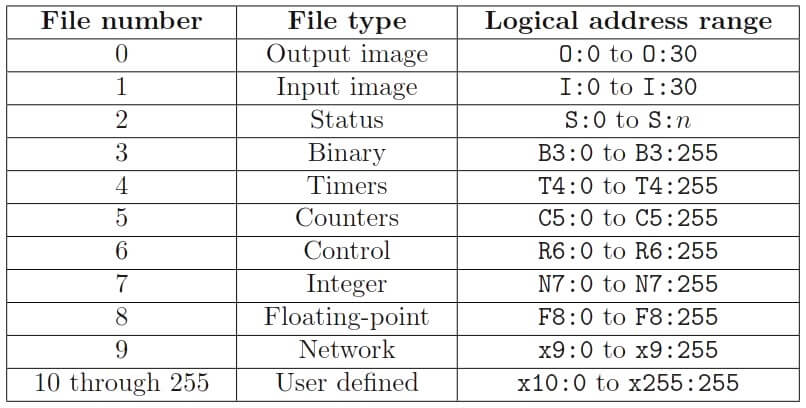

The post-obit table shows a fractional retentiveness map for an Allen-Bradley SLC 500 PLC

Retentiveness Map also called the information table, this map shows the addressing of retentiveness areas reserved for programs entered by the user. Other areas of retention exist within the SLC 500 processor, just these other areas are inaccessible to the technician writing PLC programs.

Notation that Allen-Bradley's use of the word "file" differs from personal figurer parlance. In the SLC 500 controller, a "file" is a cake of random-access retentiveness used to store a particular blazon of data.

By contrast, a "file" in a personal computer is a face-to-face collection of data bits with collective significant (e.thou. a word processing file or a spreadsheet file), usually stored on the computer'due south hd.

Within each of the Allen-Bradley PLC's "files" are multiple "elements," each element consisting of a set of bits (8, xvi, 24, or 32) representing data.

Elements are addressed by number post-obit the colon after the file designator, and individual $.25 inside each chemical element addressed by a number following a slash mark. For case, the first chip (flake 0) of the 2d element in file iii (Binary) would be addressed as B3:2/0.

In Allen-Bradley PLCs such equally the SLC 500 and PLC-v models, files 0, 1, and ii are exclusively reserved for discrete outputs, discrete inputs, and status bits, respectively.

Thus, the letter designators O, I, and S (file types) are redundant to the numbers 0, 1, and 2 (file numbers).

Other file types such as B (binary), T (timers), C (counters), and others have their own default file numbers (three, 4, and 5, respectively), merely may besides be used in some of the user-defined file numbers (x and above).

For example, file seven in an Allen-Bradley controller is reserved for information of the "integer" blazon (Northward), but integer data may besides be stored in whatsoever file numbered 10 or greater at the user's discretion.

Thus, file numbers and file type letters for information types other than output (O), input (I), and status (South) always appear together.

You lot would not typically come across an integer word addressed as N:30 (integer word 30 in the PLC'south retentiveness) for example, but rather as N7:30 (integer word 30 in file 7 of the PLC's retentiveness) to distinguish it from other integer word 30's that may be in other files of the PLC's memory.

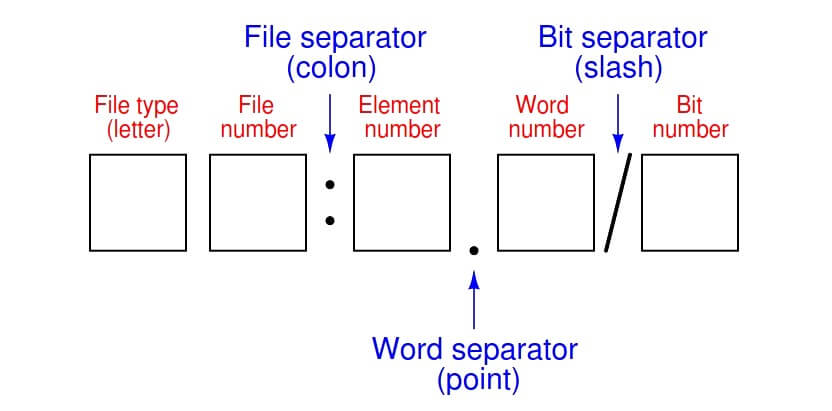

This file-based addressing notation bears further explanation. When an address appears in a PLC program, special characters are used to split (or "delimit") different fields from each other.

The general scheme for Allen-Bradley SLC 500 PLCs is shown here:

Not all file types need to distinguish private words and bits. Integer files (N), for example, consist of one 16-fleck word for each element. For case, N7:v would be the sixteen-fleck integer word number five held in file seven.

A discrete input file type (I), though, needs to be addressed as individual bits because each separate I/O point refers to a single bit. Thus, I:three/seven would be bit number seven residing in input chemical element three.

The "slash" symbol is necessary when addressing discrete I/O $.25 because we do not wish to refer to all 16 bits in a word when we just hateful a single input or output indicate on the PLC.

Integer numbers, by dissimilarity, are collections of sixteen bits each in the SLC 500 memory map, and so are usually addressed as entire words rather than fleck-by-bit .

Sure file types such as timers are more complex. Each timer "chemical element " consists of 2 different xvi-chip words (one for the timer'due south accumulated value, the other for the timer's target value) in addition to no less than 3 $.25 declaring the status of the timer (an "Enabled" fleck, a "Timing" bit, and a "Done" chip).

Thus, we must make utilize of both the decimal-point and slash separator symbols when referring to data within a timer. Suppose we declared a timer in our PLC plan with the address T4:2, which would be timer number ii independent in timer file 4.

If we wished to address that timer's current value, we would do and so as T4:2.ACC (the "Accumulator" word of timer number ii in file four). The "Done" chip of that same timer would be addressed as T4:2/DN (the "Done" bit of timer number two in file four)

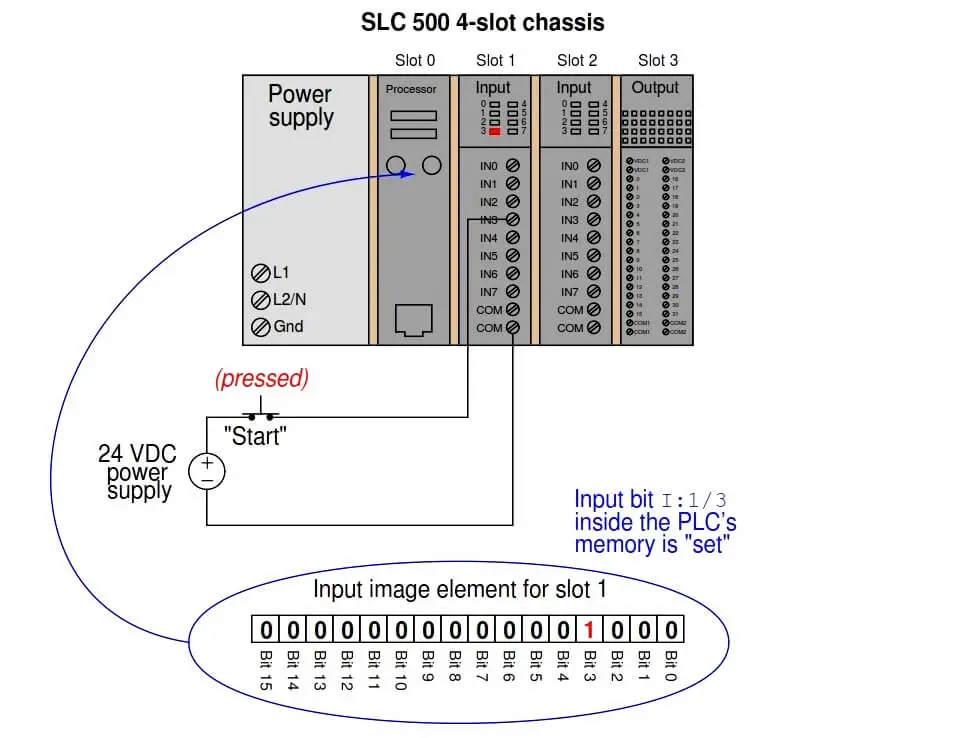

A hallmark of the SLC 500's addressing scheme common to many legacy PLC systems is that the accost labels for input and output bits explicitly reference the physical locations of the I/O channels.

For instance, if an viii-aqueduct discrete input bill of fare were plugged into slot four of an Allen Bradley SLC 500 PLC, and y'all wished to specify the second flake (scrap one out of a 0 to 7 range), you would address it with the following label: I:4/1.

Addressing the seventh bit (bit number 6) on a detached output card plugged into slot three would require the label O:3/six. In either case, the numerical structure of that label tells yous exactly where the existent-world input signal connects to the PLC.

PLC Retention Mapping Example

To illustrate the relationship betwixt physical I/O and bits in the PLC's memory, consider this example of an Allen-Bradley SLC 500 PLC, showing one of its discrete input channels energized (the switch being used equally a "Get-go" switch for an electric motor):

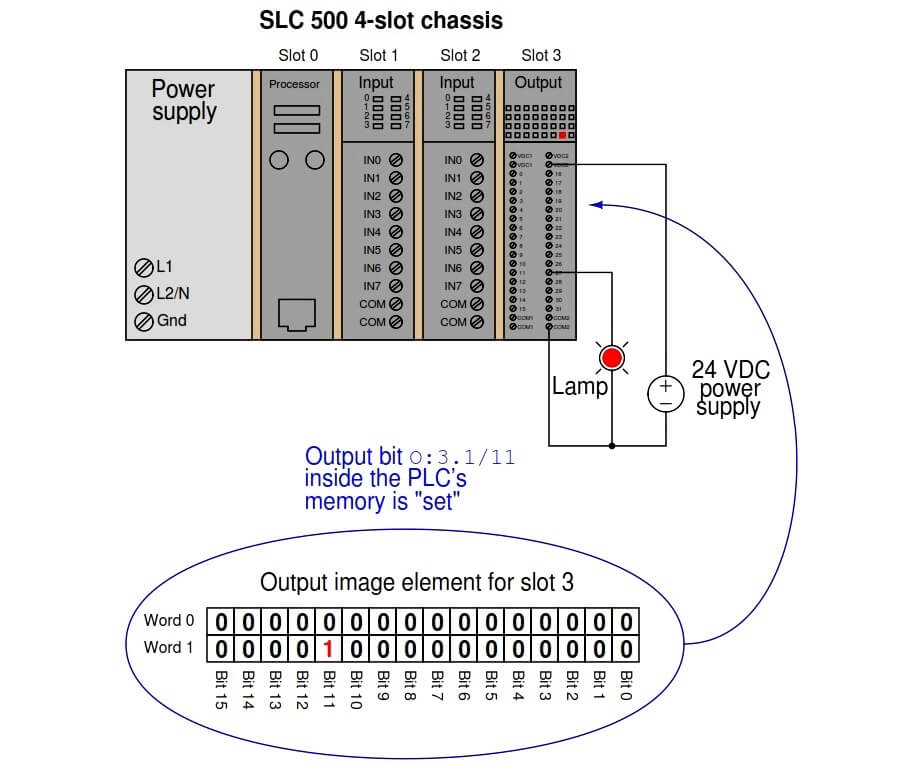

If an input or output card possesses more than xvi bits – equally in the case of the 32-bit detached output card shown in slot iii of the example SLC 500 rack – the addressing scheme farther subdivides each element into words and $.25 (each "word" being 16 bits in length).

Thus, the address for flake number 27 of a 32-bit input module plugged into slot three would be I:three.1/11 (since bit 27 is equivalent to bit 11 of give-and-take 1 – word 0 addressing bits 0 through 15 and word 1 addressing bits xvi through 31):

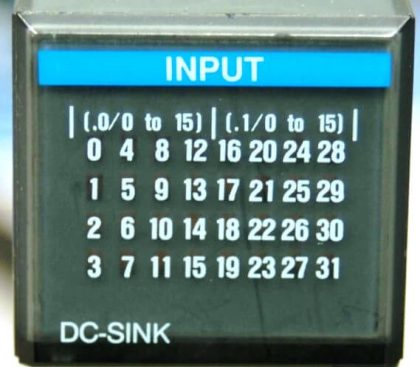

A close-up photograph of a 32-fleck DC input menu for an Allen-Bradley SLC 500 PLC organisation shows this multi-give-and-take addressing:

The first sixteen input points on this card (the left-hand LED group numbered 0 through 15) are addressed I:X.0/0 through I:X.0/15, with "10" referring to the slot number the card is plugged into. The side by side sixteen input points (the right-hand LED group numbered 16 through 31) are addressed I:X.ane/0 through I:10.one/15.

Legacy PLC systems typically reference each ane of the I/O channels by labels such as "I:ane/3" (or equivalent ) indicating the bodily location of the input channel terminal on the PLC unit.

The IEC 61131-iii programming standard refers to this aqueduct-based addressing of I/O information points as direct addressing. A synonym for straight addressing is absolute addressing.

Addressing I/O $.25 directly by their card, slot, and/or terminal labels may seem uncomplicated and elegant, but it becomes very cumbersome for big PLC systems and complex programs.

Every time a technician or programmer views the program, they must "translate" each of these I/O labels to some real-world device (due east.g. "Input I:one/three is really the Beginning push-push for the middle tank mixer motor") in order to understand the function of that flake.

A later effort to enhance the clarity of PLC programming was the concept of addressing variables in a PLC'southward retentivity by arbitrary names rather than fixed codes.

The IEC 61131-three programming standard refers to this as symbolic addressing in contrast to "direct" (aqueduct-based) addressing, allowing programmers arbitrarily name I/O channels in ways that are meaningful to the arrangement equally a whole.

To employ our unproblematic motor "Start" switch example, information technology is now possible for the programmer to designate input I:1/iii (an instance of a direct address) every bit "Motor start switch" (an example of a symbolic accost) within the program, thus greatly enhancing the readability of the PLC program.

Initial implementations of this concept maintained direct addresses for I/O data points, with symbolic names appearing as supplements to the absolute addresses.

The modernistic trend in PLC addressing is to avert the utilize of straight addresses such as I:1/3 altogether, so they do not appear anywhere in the programming code.

The Allen-Bradley "Logix" series of programmable logic controllers is the most prominent instance of this new convention at the time of this writing.

Each I/O betoken, regardless of type or physical location, is assigned a tag proper noun which is meaningful in a real-earth sense, and these tag names (or symbols as they are alternatively called) are referenced to absolute I/O aqueduct locations by a database file.

An of import requirement of tag names is that they contain no space characters between words (due east.g. instead of "Motor outset switch", a tag name should use hyphens or underscore marks as spacing characters: "Motor outset switch"), since spaces are by and large assumed by computer programming languages to be delimiters (separators between different variables).

Having introduced Allen-Bradley's addressing notation for SLC 500 model PLCs, I will now abandon it in favor of the modernistic convention of symbolic addressing throughout the rest of the articles, so equally to avoid making the programming examples brand- or model-specific. Each data point within my PLC programs will acquit its own tag name rather than a direct (aqueduct-based) address characterization.

Credits : by Tony R. Kuphaldt – Artistic Commons Attribution 4.0 License

PLC Tutorials :

-

What is Programmable Logic Controller ?

-

What is Ladder Diagram Programming ?

-

History of Programmable Logic Controllers

-

Mis-conceptions of PLC Ladder Logic

-

Contacts and coils in PLC

-

Digital Input and Output Modules

-

Analog I/O and Network I/O

-

PLC Input/Output Modules

-

Memory Mapping in PLC

-

Analog Input Scaling

-

PLC Instance with Switches

-

Counter Instructions

-

Timer Instructions

-

Math instructions

-

Data Instructions

-

Ladder Logic Questions

If you lot liked this article, and then please subscribe to our YouTube Aqueduct for PLC and SCADA video tutorials.

Yous can also follow united states of america on Facebook and Twitter to receive daily updates.

Share With Your Friends

You've successfully subscribed !

Can Slc500 Ch. 0 Registers,

Source: https://instrumentationtools.com/plc-memory-mapping-io-addressing/

Posted by: carterseved1952.blogspot.com

0 Response to "Can Slc500 Ch. 0 Registers"

Post a Comment